# **S1.26**

# 2D MoS, Transistors

MARC2024 Microsystems Annual Research Conference

#### Bianca Hanly, Lucas Ospina, Sanjay Seshan, Dip Joti Paul PI: Farnaz Niroui

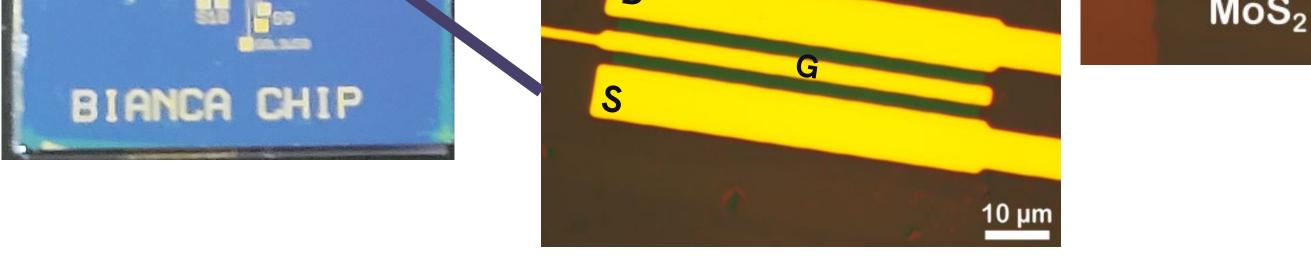

**Transfer Characteristics**

Electrical Engineering & Computer Science, Massachusetts Institute of Technology, 6.2540 Course Project

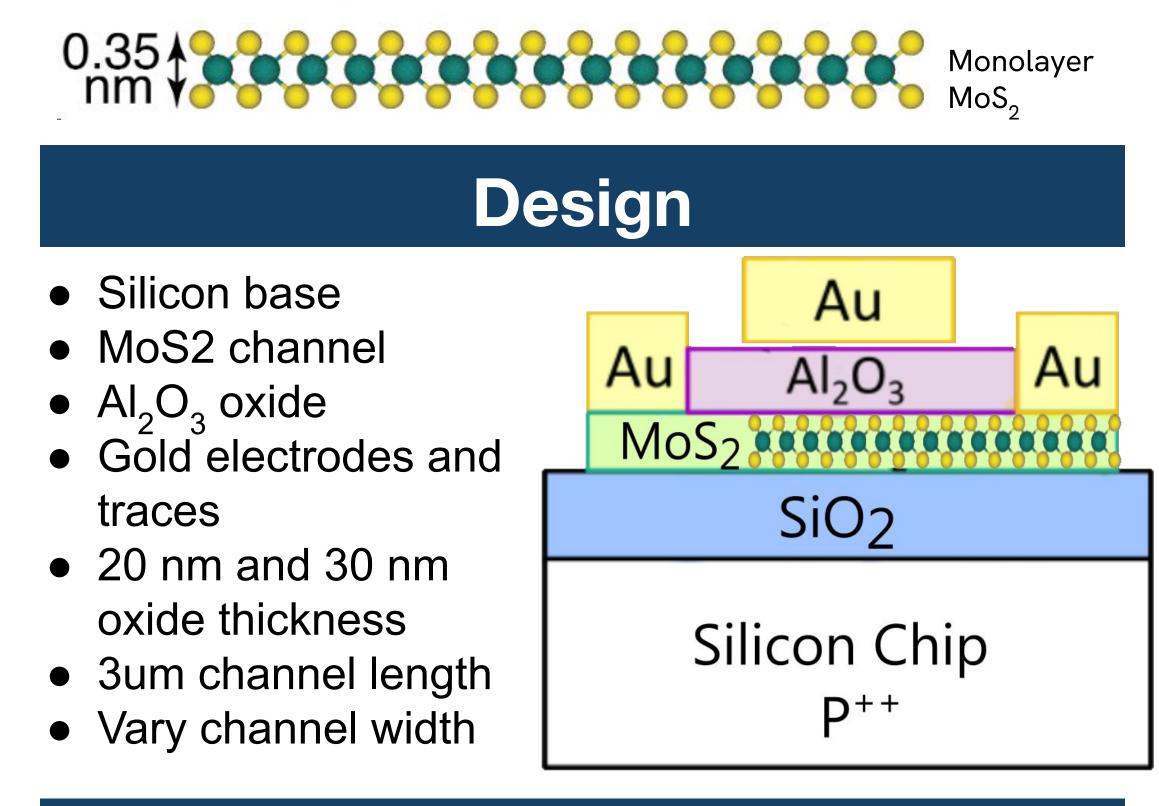

| Introduction                                                                                                                                                                                                                                                                       | Results                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <ul> <li>Background:</li> <li>Approaching the end of Moore's law <ul> <li>Shrinking traditional silicon transistors to improve performance is getting harder because of quantum tunnelling</li> </ul> </li> <li>2D materials <ul> <li>Diverse functionality</li> </ul> </li> </ul> | SiO <sub>2</sub><br>AlO <sub>3</sub><br>B<br>MOS <sub>2</sub> 10 μm |

- Diverse functionality

- Better electronic properties

- Allow for flexible form factors

#### Goal:

- Fabricate a MOSFET using MoS<sub>2</sub> instead of Si

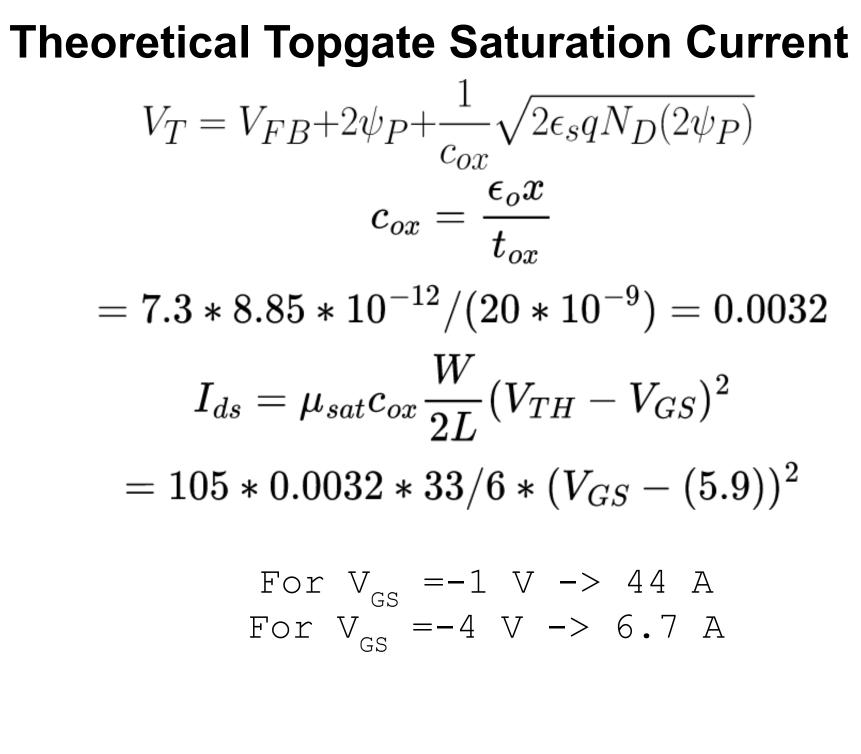

- Implement a top-gate approach

- Characterize transistor performance

# **Output Characteristic**

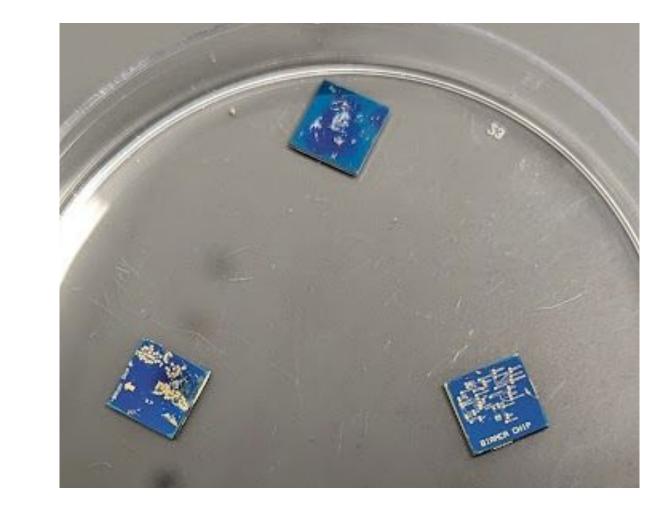

- We had dozens of transistors across 4 chips

- Presented are samples from chip B

- Back gate and Top gate results are as expected for an NMOS transistor • Threshold voltages are calculated and drawn on the graphs

## **MoS2 Transistor Fabrication**

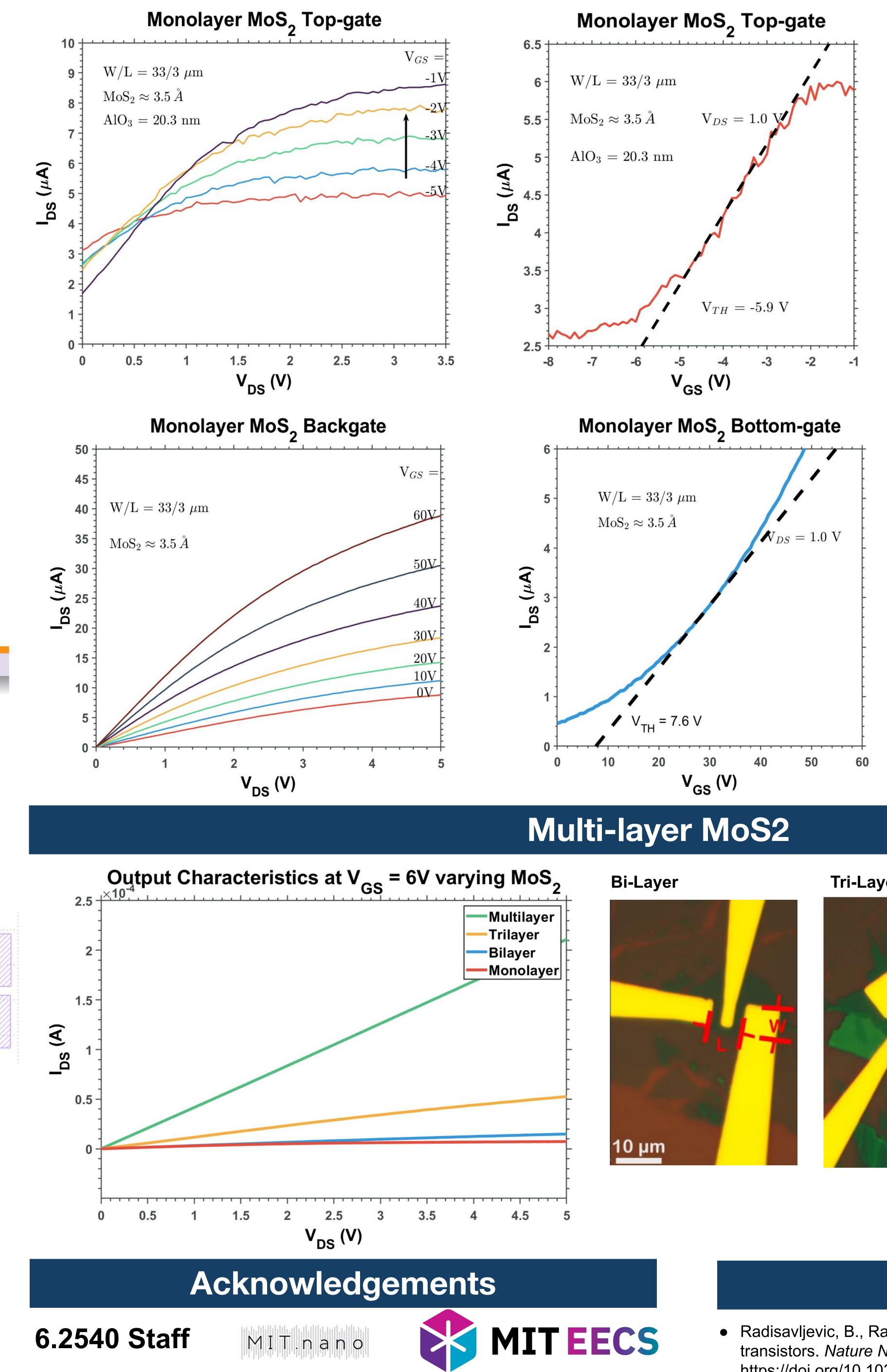

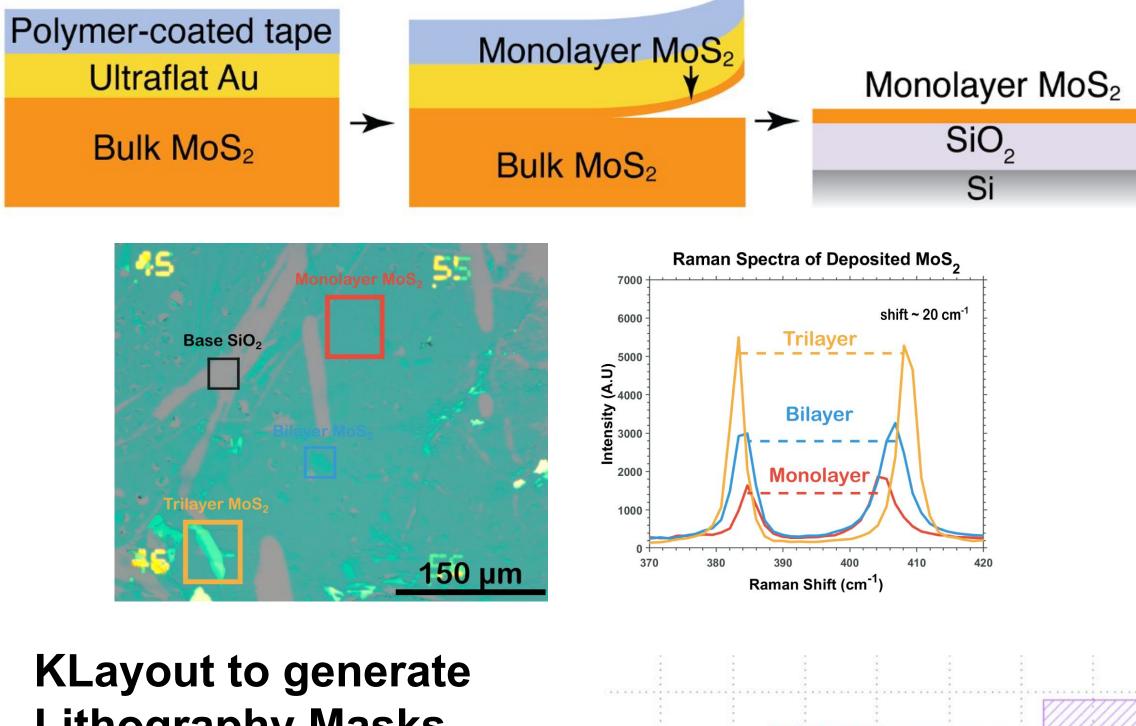

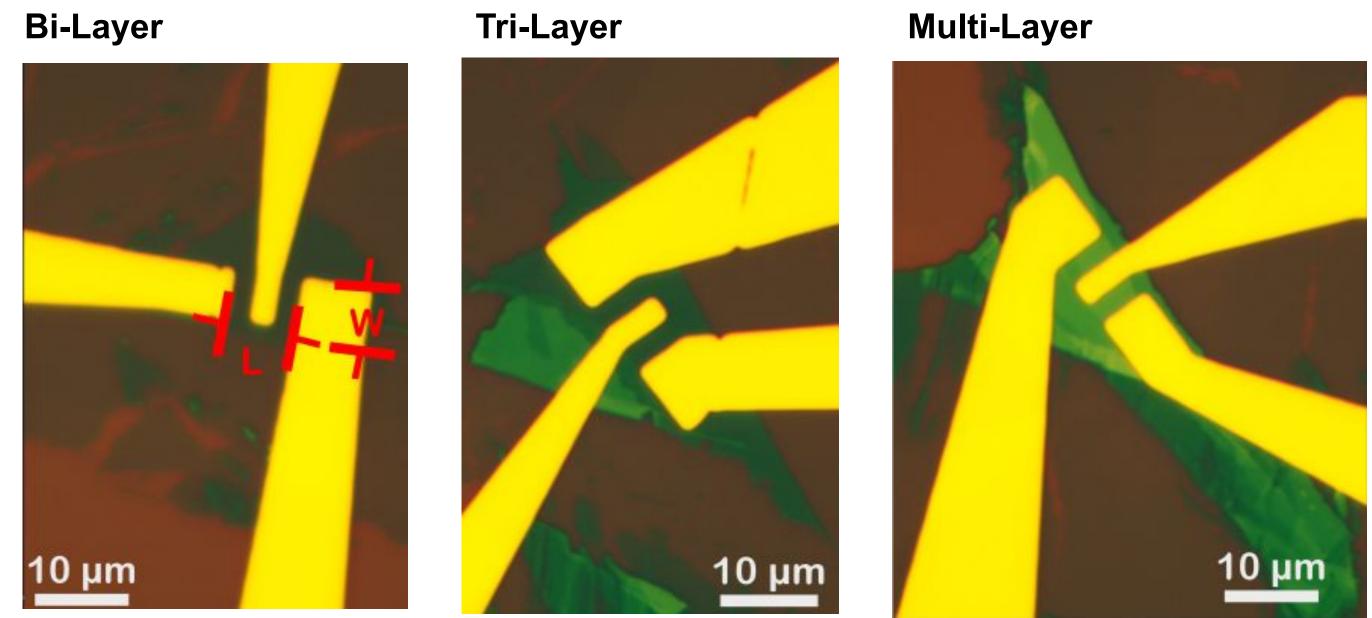

#### **Gold-Mediated MoS2 exfoliation**

- Van Der Waals interactions from special polymer is good for picking up large monolayer patches

- Contiguous patches ~100um in each dimension

- Monolayer, Bilayer, and Trilayer patches

• Results are very promising

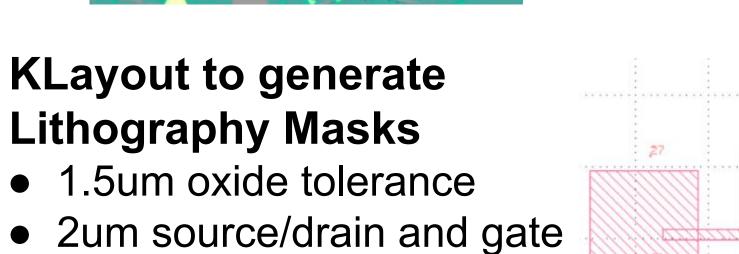

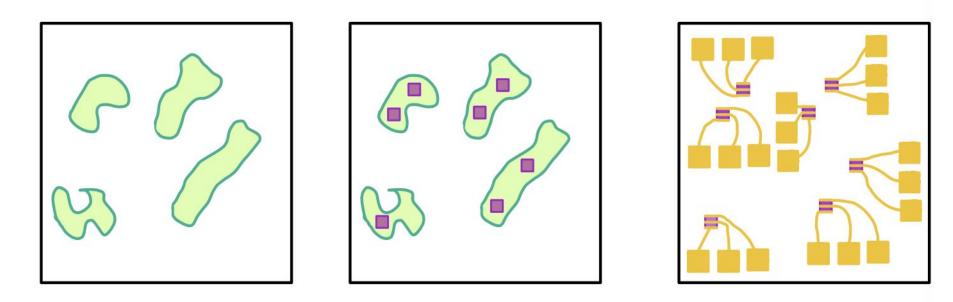

- distance

- 20um traces

- 300x300um contact pads

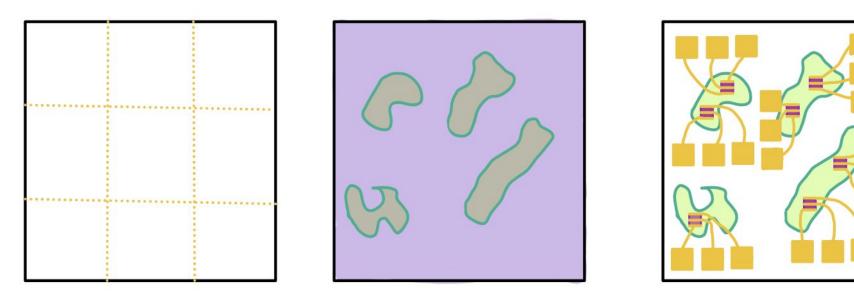

1. Original substrate 3. ALD Deposition 5. Electrodes

2. MoS2 Exfoliation 4. Oxide Lithography 6. MoS2 Etching

Special thanks to Sarah Spector and Farnaz Niroui for their contributions

### References

- Radisavljevic, B., Radenovic, A., Brivio, J. *et al.* Single-layer MoS<sub>2</sub> transistors. Nature Nanotech 6, 147–150 (2011). https://doi.org/10.1038/nnano.2010.279

- Gold mediated MoS2 figure from S1.15 of last years conference

- All other figures are drawn or generated by the authors